APPLICATION MANUAL RV-4162

62

**Application Manual**

# Ultra Small

# Real Time Clock / Calendar Module with 12C Interface

| Date: January 2014                   |               |                  |          | Revision N°: 2.1       |

|--------------------------------------|---------------|------------------|----------|------------------------|

|                                      |               |                  |          | 1/39                   |

|                                      | Headquarters: | Micro Crystal AG | Tel.     | +41 32 655 82 82       |

|                                      |               | Mühlestrasse 14  | Fax      | +41 32 655 82 83       |

|                                      |               | CH-2540 Grenchen | Internet | www.microcrystal.com   |

| A COMPANY OF THE <b>SWATCH GROUP</b> |               | Switzerland      | Email    | sales@microcrystal.com |

# **TABLE OF CONTENTS**

| 1. | OVE                | RVIEW                                      | 4  |

|----|--------------------|--------------------------------------------|----|

|    | 1.1.               | GENERAL DESCRIPTION                        | 4  |

|    | 1.2.               | APPLICATIONS                               | 4  |

| 2. | BLC                | OCK DIAGRAM                                | 5  |

|    | 2.1.               | PINOUT                                     | 6  |

|    | 2.2.               | PIN DESCRIPTION                            | 6  |

|    | 2.3.               | FUNCTIONAL DESCRIPTION                     | 6  |

|    | 2.4.               | DEVICE PROTECTION DIAGRAM                  | 7  |

| 3. | REG                | SISTER ORGANIZATION                        | 8  |

|    | 3.1.               | REGISTER ACCESS                            | 8  |

|    | 3.2.               | BUFFER / TRANSFER REGISTERS                | 9  |

|    | 3.3.               | REGISTER OVERVIEW                          | 10 |

|    | 3.4.               | CLOCK SECTION                              | 11 |

|    | 3.5.               | CONTROL SECTION                            | 13 |

|    | 3.6.               | DATA FLOW OF TIME AND DATE FUNCTION        | 15 |

|    | 3.7.               | REGISTER RESET VALUE                       | 15 |

| 4. | DET                | AILED FUNCTIONAL DESCRIPTION               | 16 |

|    | 4.1.               | CLKOUT FREQUENCY SELECTION                 | 16 |

|    | 4.2.               | FREQUENCY OFFSET COMPENSATION              | 17 |

|    | 4.                 | 2.1. FREQUENCY OFFSET COMPENSATION METHOD  | 18 |

|    | 4.                 | 2.2. DEFINING FREQUENCY COMPENSATION VALUE | 19 |

|    | 4.3.               | WATCHDOG TIMER                             | 20 |

|    | 4.4.               | ALARM FUNCTION                             | 21 |

|    | 4.5.               | CENTURY BITS                               | 22 |

|    | 4.6.               | LEAP YEAR                                  | 22 |

|    | 4.7.               | OSCILLATOR STOP DETECTION                  | 23 |

|    | 4.8.               | OUTPUT DRIVER PIN                          | 23 |

| 5. | CHA                | RACTERISTICS OF THE I <sup>2</sup> C BUS   | 24 |

|    | 5.1.               | BIT TRANSFER                               | 24 |

|    | 5.2.               | START AND STOP CONDITIONS                  | 24 |

|    | 5.3.               | SYSTEM CONFIGURATION                       | 25 |

|    | 5.4.               | ACKNOWLEDGE                                | 25 |

| 6. | I <sup>2</sup> C E | BUS PROTOCOL                               | 26 |

|    | 6.1.               | ADDRESSING                                 | 26 |

|    | 6.2.               | CLOCK AND CALENDAR READ AND WRITE CYCLES   | 26 |

|    | 6.                 | 2.1. WRITE MODE                            | 26 |

|    | 6.                 | 2.2. READ MODE AT SPECIFIC ADDRESS         | 27 |

|    | 6.                 | 2.3. READ MODE                             | 27 |

| 7. | ELE  | CTRICAL CHARACTERISTICS                                                 | 8 |

|----|------|-------------------------------------------------------------------------|---|

|    | 7.1. | ABSOLUTE MAXIMUM RATINGS                                                | 8 |

|    | 7.2. | OPERATING AND AC MEASUREMENTS CONDITIONS                                | 8 |

|    |      | CAPACITANCE                                                             |   |

|    | 7.4. | FREQUENCY CHARACTERISTICS                                               | 9 |

|    | 7.5. | FREQUENCY VS. TEMPERATURE CHARACTERISTICS                               | 9 |

|    | 7.6. | STATIC CHARACTERISTICS                                                  | 0 |

|    | 7.7. | <sup>2</sup> C INTERFACE TIMING CHARACTERISTICS                         | 1 |

| 8. | APP  | PLICATION INFORMATION                                                   | 2 |

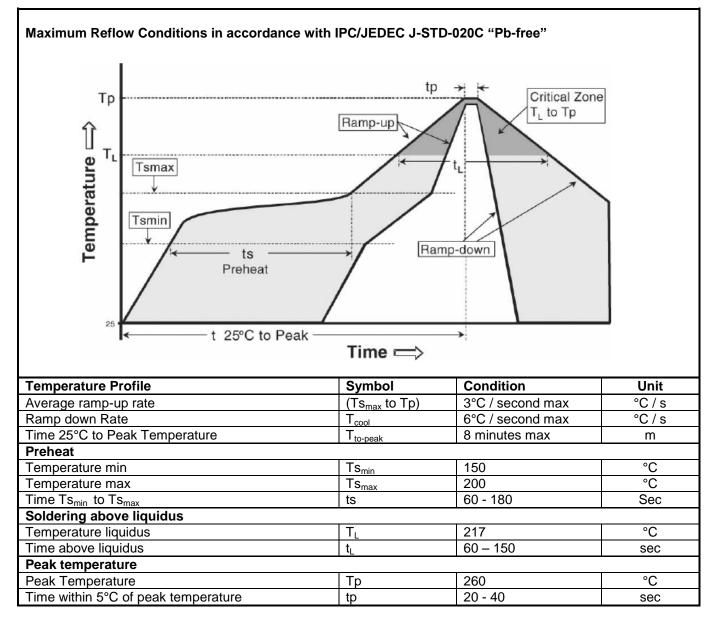

|    | 8.1. | RECOMMENDED REFLOW TEMPERATURE (LEADFREE SOLDERING)                     | 3 |

| 9. | PAC  | CKAGES                                                                  | 4 |

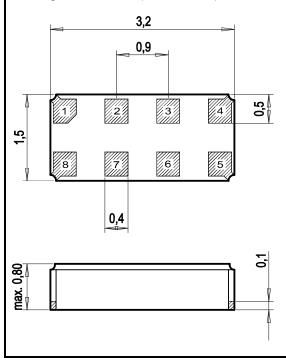

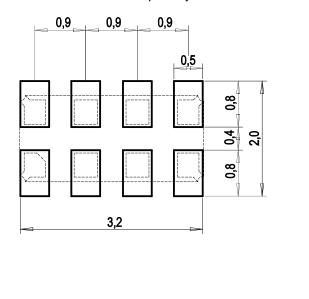

|    |      | DIMENSIONS AND SOLDERPADS LAYOUT                                        |   |

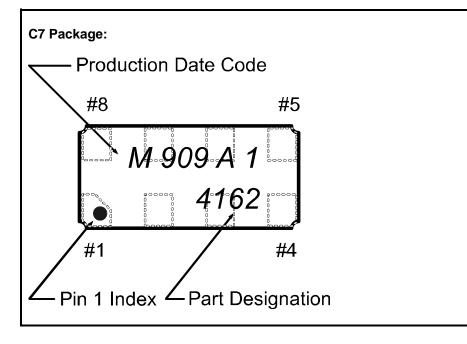

|    |      | MARKING AND PIN #1 INDEX                                                |   |

| 10 |      | KING INFORAMTION                                                        |   |

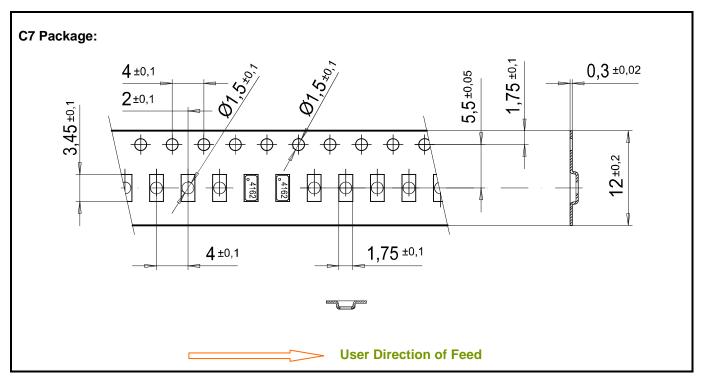

|    |      | . CARRIER TAPE                                                          |   |

|    | -    | . PARTS PER REEL                                                        |   |

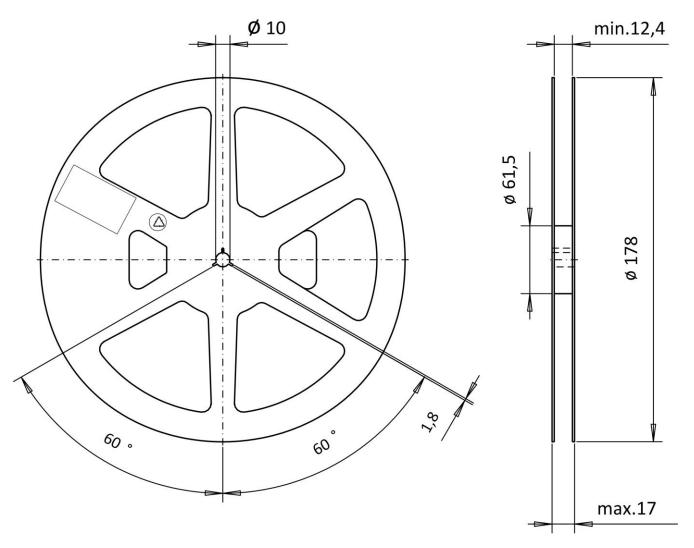

|    | 10.3 | . REEL 7 INCH FOR 12 mm TAPE                                            | 7 |

|    | 10.4 | . HANDLING PRECAUTIONS FOR CRYSTALS OR MODULES WITH EMBEDDED CRYSTALS 3 | 8 |

| 11 | .DOC | CUMENT REVISION HISTORY                                                 | 9 |

# RV-4162

# Ultra Small Real Time Clock / Calendar Module with I<sup>2</sup>C Interface

# 1. OVERVIEW

- RTC module with built-in "Tuning Fork" crystal oscillating at 32.768 kHz

- Serial RTC with alarm functions:

- 400 kHz I<sup>2</sup>C serial interface

- Memory mapped registers for seconds, minutes, hours, day, date, month, year and century

- Tenths / hundredths of seconds register

- 350 nA timekeeping current at 3.0 V

- Timekeeping down to 1.0 V

- 1.3 V to 4.4 V I<sup>2</sup>C bus operating voltage

- Low operating current of 35  $\mu$ A (f<sub>SCL</sub> = 400 kHz)

- 32.768 kHz square wave output available at power-up, suitable for driving a uC in low power mode (can be disabled)

- Programmable 1 Hz to 32.768 kHz square wave output

- Programmable alarm with interrupt function

- Oscillator stop detection monitors clock operation

- Accurate programmable watchdog: 62.5 ms to 31 min timeout

- Software clock calibration, can adjust timekeeping within +/-2 ppm

- Automatic leap year compensation

- Operating temperature range: -40°C to +85°C

- Ultra small and compact C7 package size, RoHS-compliant and 100% leadfree: 3.2 x 1.5 x 0.8 mm

# 1.1. GENERAL DESCRIPTION

The RV-4162 is a low power serial Real Time Clock (RTC) module with built-in 32.768 kHz crystal (no external components are required for the oscillator). Eight registers are used for the clock / calendar function and are configured in binary coded decimal (BCD) format. An additional 8 registers provide status / control of alarm, calibration, programmable square wave output and watchdog functions. Addresses and data are transferred serially via a two line, bidirectional  $I^2C$  interface. The built-in address register is incremented automatically after each WRITE or READ data byte.

Functions available to the user include a time-of-day clock / calendar, alarm interrupts, programmable square wave output, and watchdog. The eight clock address locations contain the century, year, month, date, day, hour, minute, second and tenths / hundredths of a second in 24-hour BCD format. Corrections for 28, 29 (leap year), 30 and 31 day months are made automatically.

# 1.2. APPLICATIONS

The RV-4162 RTC module combines standard RTC functions in high reliable, ultra-small ceramic package:

- Smallest RTC module (embedded XTAL) in an ultra-small 3.2 x 1.5 x 0.8 mm leadfree ceramic package.

- Price competitive

The unique size and the competitive pricing make this product perfectly suitable for many applications:

- Automotive: Navigation & Tracking Systems / Dashboard / Tachometers / Car Audio & Entertainment Systems

- Metering: E-Meter / Heating Counter / Smart Meters / PV Converter

- Outdoor: ATM & POS systems / Ticketing Systems

- Medical: Glucose Meter / Health Monitoring Systems

- Safety: Security & Camera Systems / Door Lock & Access Control

- Consumer: Gambling Machines / TV & Set Top Boxes / White Goods

- Automation: Data Logger / Home & Factory Automation / Industrial and Consumer Electronics

### RV-4162

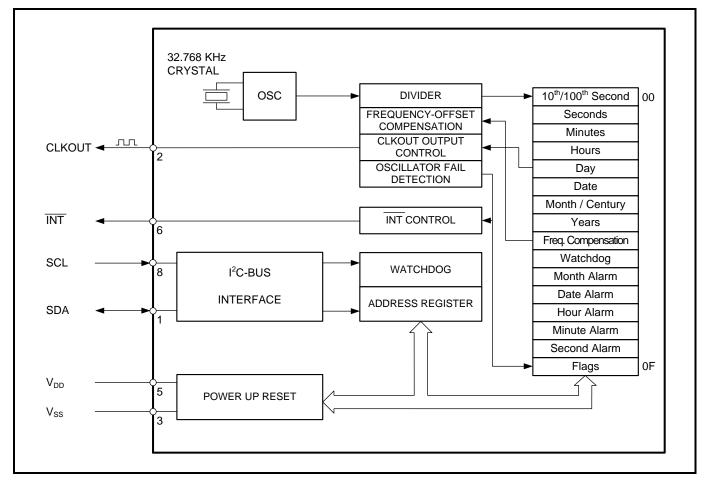

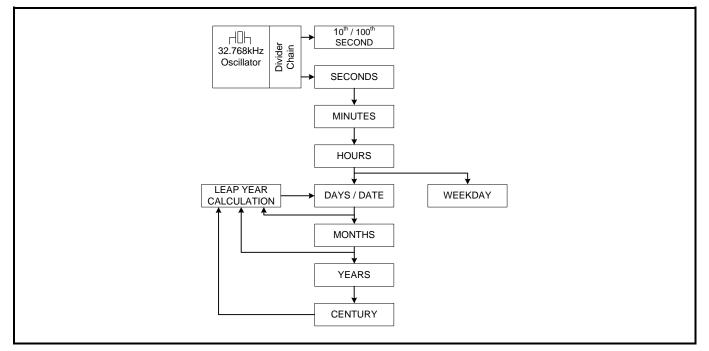

# 2. BLOCK DIAGRAM

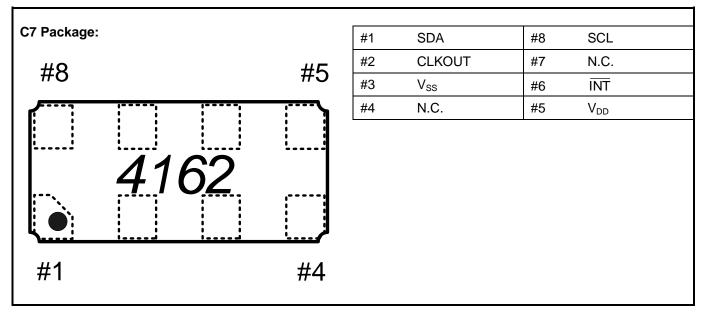

# 2.1. PINOUT

### 2.2. PIN DESCRIPTION

| Symbol          | Pin # | Description                                                         |

|-----------------|-------|---------------------------------------------------------------------|

| SDA             | 1     | Serial Data; open-drain; requires pull-up resistor                  |

| CLKOUT          | 2     | Clock Output                                                        |

| V <sub>SS</sub> | 3     | Ground                                                              |

| N.C.            | 4     | Not Connected                                                       |

| V <sub>DD</sub> | 5     | Power Supply Voltage                                                |

| INT             | 6     | Interrupt Output; open-drain; requires pull-up resistor; active low |

| N.C.            | 7     | Not Connected                                                       |

| SCL             | 8     | Serial Clock Input; requires pull-up resistor                       |

# 2.3. FUNCTIONAL DESCRIPTION

The RV-4162 is a low power CMOS Real-Time Clock / Calendar module with built-in "Tuning-Fork" crystal with the nominal frequency of 32.768 kHz; no external components are required for the oscillator circuitry.

The oscillator frequency on all devices is tested not to exceed a time deviation of  $\pm 20$  ppm (parts per million) at 25°C, which equates to about  $\pm 52$  seconds per month.

This time accuracy can be further improved to  $\pm 2$  ppm at 25°C or better by individually measuring the frequencydeviation in the application and programming a correction value into the frequency compensation register.

The CMOS IC contains 16 8-bit RAM registers; the address counter is automatically incremented after each written or read data byte. All sixteen registers are designed as addressable 8-bit parallel registers, although, not all bits are implemented.

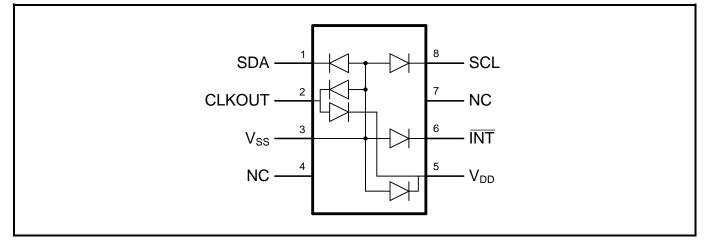

# 2.4. DEVICE PROTECTION DIAGRAM

# 3. REGISTER ORGANIZATION

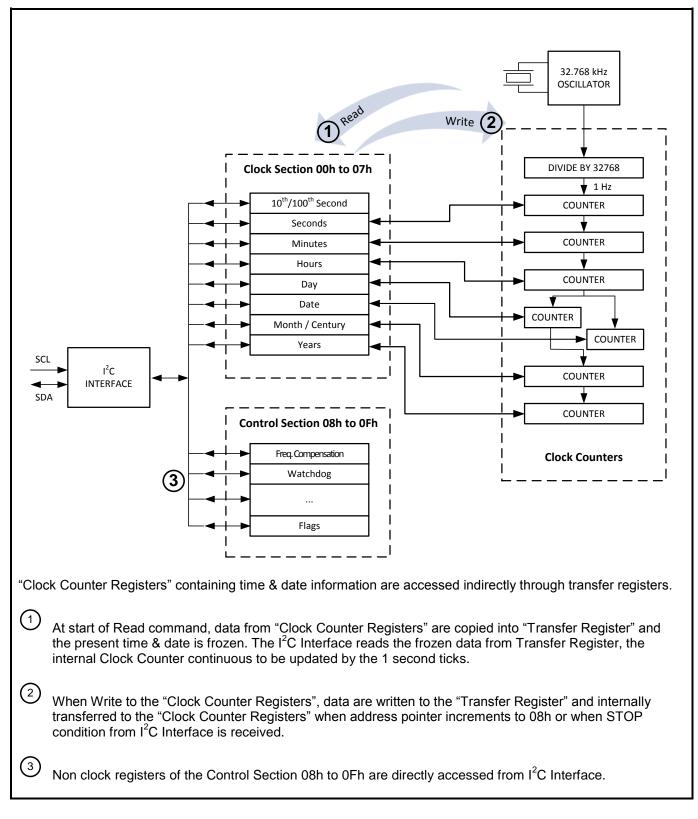

The RV-4162 user interface consists of 16 memory mapped registers which include clock, calibration, alarm, watchdog, flags, and square wave control.

First 8 registers are the Clock Section at address 00h through 07h. These registers are accessed indirectly via a set of transfer registers.

### Clock Section (addresses 00h through 07h):

These registers are coded in BCD format and contain the century, year, month, day / date, hours, minutes, seconds and tenths / hundredths of seconds in 24-hour format. Corrections for 28, 29 (leap year), 30 or 31 day of months are made automatically. These registers are accessed indirectly through transfer registers.

Next 8 registers are the control section at address 08h through 0Fh.

### Control Section (addresses 08h through 0Fh):

These registers are coded in binary format and provide status, frequency compensation, alarm and control of the peripheral functions including the programmable clock output and watchdog functions.

The CMOS IC contains 16 8-bit RAM registers. These registers are carried out double: internal counters and external user accessible registers.

All sixteen registers are designed as addressable 8-bit parallel registers, although, not all bits are implemented. The address counter is automatically incremented after each written or read data byte.

The internal registers keeping track of the time based on the 32.768 kHz clock oscillator and the divider chain. The external registers are independent of the internal counters except that they are updated periodically by the simultaneous transfer of the incremented internal data. To prevent data transition during Interface access, the content of the external register is kept stable whenever the address being read is a clock address (00h to 07h). The update of the external register will resume either when the address-pointer increments to a non-clock address or Interface communication is terminated by sending a "STOP condition".

After "WRITE" to the external register, when the "STOP condition" terminates the Interface communication, the content of the modified external registers is copied into the corresponding internal registers. The divider chain of the 32.768 kHz oscillator will be reset upon the completion of a "WRITE" to any clock address (00h to 07h).

### 3.1. REGISTER ACCESS

During normal operation when the user is not accessing the device, the transfer registers are kept updated with a copy of the Clock Counter data.

At the start of an  $I^2C$  read or write cycle, the updating is halted and the present time & date is frozen in the transfer registers. Halting the updates at the start of an  $I^2C$  access is to ensure that all the time & date data transferred out during a read sequence comes from the same instant in time.

When writing to the device, each bit is shifted into the RV-4162's  $I^2C$  Interface on the rising edge of the SCL signal. On the 8th clock cycle, each byte is transferred from the  $I^2C$  block into the register addressed by the address pointer.

Data written to the Clock Registers (addresses 00h - 07h) is held in the transfer registers until the address pointer increments to 08h, or when STOP condition from I<sup>2</sup>C Interface is received. At which time the data in the transfer registers are simultaneously copied into the Clock Counters and then the clock is restarted.

### 3.2. BUFFER / TRANSFER REGISTERS

### 3.3. REGISTER OVERVIEW

### Clock Section (addresses 00h through 07h):

These registers are coded in BCD format and contain the century, year, month, day / date, hour, minute, second and tenths/hundredths of a second in 24-hour format. Corrections for 28, 29 (leap year), 30 or 31 day months are made automatically. These registers are accessed indirectly through transfer registers.

### Control Section (addresses 08h through 0Fh):

These registers are coded in binary format and provide status, frequency compensation, alarm and control of the peripheral functions incl. the programmable clock-output and watchdog functions.

| Address | Function                                    | Bit 7 | Bit 6               | Bit 5  | Bit 4 | Bit 3                       | Bit 2 | Bit 1 | Bit 0 |  |

|---------|---------------------------------------------|-------|---------------------|--------|-------|-----------------------------|-------|-------|-------|--|

| 00h     | 10 <sup>th</sup> / 100 <sup>th</sup> Second |       | 10 <sup>th</sup> of | Second | •     | 100 <sup>th</sup> of Second |       |       |       |  |

| 001     | 10 / 100 Second                             | 8     | 4                   | 2      | 1     | 8                           | 4     | 2     | 1     |  |

| 01h     | Seconds                                     | OS    | 40                  | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 02h     | Minutes                                     | OFIE  | 40                  | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 03h     | Hours                                       | 0     | 0                   | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 04h     | Day                                         | FD3   | FD2                 | FD1    | FD0   | 0                           | 4     | 2     | 1     |  |

| 05h     | Date                                        | 0     | 0                   | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 06h     | Month / Century                             | CB1   | CB0                 | 0      | 10    | 8                           | 4     | 2     | 1     |  |

| 07h     | Years                                       | 80    | 40                  | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 08h     | Freq. Compensation                          | OUT   | 0                   | Mode   | 16    | 8                           | 4     | 2     | 1     |  |

| 09h     | Watchdog                                    | WD2   | WDM4                | WDM3   | WDM2  | WDM1                        | WDM0  | WD1   | WD0   |  |

| 0Ah     | Month Alarm                                 | AFE   | CLKOE               | 0      | 10    | 8                           | 4     | 2     | 1     |  |

| 0Bh     | Date Alarm                                  | ARM4  | ARM5                | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 0Ch     | Hour Alarm                                  | ARM3  | 0                   | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 0Dh     | Minute Alarm                                | ARM2  | 40                  | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 0Eh     | Second Alarm                                | ARM1  | 40                  | 20     | 10    | 8                           | 4     | 2     | 1     |  |

| 0Fh     | Flags                                       | WDF   | AF                  | 0      | 0     | 0                           | OF    | 0     | 0     |  |

Bit positions labelled with 0 should always be written with logic "0".

# 3.4. CLOCK SECTION

# 10<sup>th</sup> / 100<sup>th</sup> Second (address 00h...bits description)

| Address | Function                                                      | Bit 7  | Bit 6                                                                          | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|---------------------------------------------------------------|--------|--------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 00h     | 10 <sup>th</sup> / 100 <sup>th</sup> of seconds <sup>1)</sup> | 8      | 4                                                                              | 2     | 1     | 8     | 4     | 2     | 1     |  |

| Bit     | Symbol                                                        | Value  | Description                                                                    |       |       |       |       |       |       |  |

| 7 to 4  | 10 <sup>th</sup> of second                                    | 0 to 9 | This register hold the current 10 <sup>th</sup> of second coded in BCD format  |       |       |       |       |       |       |  |

| 3 to 0  | 100 <sup>th</sup> of second                                   | 0 to 9 | This register hold the current 100 <sup>th</sup> of second coded in BCD format |       |       |       |       |       |       |  |

<sup>1)</sup> Generation of 100<sup>th</sup> and 10<sup>th</sup> of second is derived from the internal clock source 32.768 kHz divided by 328 = 0.010009766 second. A WRITE to any register of the Clock Section 00h to 07h will reset the divider chain of the 32.768 kHz clock and set the 10<sup>th</sup> / 100<sup>th</sup> of second = "00". Values other than "00" cannot be written to this register.

### Seconds (address 01h...bits description)

| Address | Function | Bit 7   | Bit 6                                                       | Bit 5        | Bit 4       | Bit 3        | Bit 2                    | Bit 1                | Bit 0 |  |

|---------|----------|---------|-------------------------------------------------------------|--------------|-------------|--------------|--------------------------|----------------------|-------|--|

| 01h     | Seconds  | OS      | 40                                                          | 20           | 10          | 8            | 4                        | 2                    | 1     |  |

| Bit     | Symbol   | Value   | Description                                                 |              |             |              |                          |                      |       |  |

| 7       | OS       | 0       | 32.768 kł                                                   | Iz oscillato | r is enable | d and starts | s within T <sub>st</sub> | $_{art} \leq 1$ sec. |       |  |

| 1       | 03       | 1       | 32.768 kHz oscillator is disabled (stopped)                 |              |             |              |                          |                      |       |  |

| 6 to 0  | Seconds  | 0 to 59 | This register holds the current seconds coded in BCD format |              |             |              |                          |                      |       |  |

### Minutes (address 02h...bits description)

| Address | Function | Bit 7   | Bit 6                                                                                                       | Bit 5                                 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|----------|---------|-------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-------|-------|-------|-------|--|--|

| 02h     | Minutes  | OFIE    | 40                                                                                                          | 20                                    | 10    | 8     | 4     | 2     | 1     |  |  |

| Bit     | Symbol   | Value   | Description                                                                                                 |                                       |       |       |       |       |       |  |  |

|         |          | 0       | Oscillator                                                                                                  | Oscillator fail interrupt is disabled |       |       |       |       |       |  |  |

| 7       | OFIE     | 1       | Oscillator fail interrupt is enabled; an interrupt will be issued when an<br>oscillator failure is detected |                                       |       |       |       |       |       |  |  |

| 6 to 0  | Minutes  | 0 to 59 | This register holds the current minutes coded in BCD format                                                 |                                       |       |       |       |       |       |  |  |

### Hours (address 03h...bits description)

| Address | Function | Bit 7   | Bit 6                                                     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|----------|---------|-----------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 03h     | Hours    | 0       | 0                                                         | 20    | 10    | 8     | 4     | 2     | 1     |  |

| Bit     | Symbol   | Value   | Description                                               |       |       |       |       |       |       |  |

| 7 to 6  | Х        | 0       | Unused; must be set to "0"                                |       |       |       |       |       |       |  |

| 5 to 0  | Hours    | 0 to 23 | This register holds the current hours coded in BCD format |       |       |       |       |       |       |  |

### RV-4162

### Day (address 04h...bits description)

| Address   | Function   | Bit 7              | Bit 6                                                                                                                      | Bit 5         | Bit 4        | Bit 3      | Bit 2     | Bit 1                  | Bit 0      |  |

|-----------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|--------------|------------|-----------|------------------------|------------|--|

| 04h       | Day        | FD3                | FD2                                                                                                                        | FD1           | FD0          | 0          | 4         | 2                      | 1          |  |

| Bit       | Symbol     | Value              |                                                                                                                            | [             |              | Reference  |           |                        |            |  |

| 7 to 4    | FD0 to FD3 | 0000<br>to<br>1111 | FD0 to FD3 bits control CLKOUT frequency<br>0000 no frequency at CLKOUT See se<br>0001 to 1111 select the CLKOUT frequency |               |              |            |           |                        | ection 4.1 |  |

| 3         | Х          | 0                  | Unused;                                                                                                                    | must be se    | t to "0"     |            |           |                        |            |  |

| 2 to 0    | Weekday    | 1 to 7             | This regis                                                                                                                 | ster holds tl | he current v | weekday co | ded in BC | D format <sup>1)</sup> |            |  |

| Weekday   |            | Bit 7              | Bit 6                                                                                                                      | Bit 5         | Bit 4        | Bit 3      | Bit 2     | Bit 1                  | Bit 0      |  |

| Sunday    |            | Х                  | Х                                                                                                                          | Х             | Х            | 0          | 0         | 0                      | 1          |  |

| Monday    |            | Х                  | Х                                                                                                                          | Х             | Х            | 0          | 0         | 1                      | 0          |  |

| Tuesday   |            | Х                  | Х                                                                                                                          | Х             | Х            | 0          | 0         | 1                      | 1          |  |

| Wednesday |            | Х                  | Х                                                                                                                          | Х             | Х            | 0          | 1         | 0                      | 0          |  |

| Thursday  | Х          | Х                  | Х                                                                                                                          | Х             | 0            | 1          | 0         | 1                      |            |  |

| Friday    |            | Х                  | Х                                                                                                                          | Х             | Х            | 0          | 1         | 1                      | 0          |  |

| Saturday  |            | Х                  | Х                                                                                                                          | Х             | Х            | 0          | 1         | 1                      | 1          |  |

<sup>1)</sup> These bits may be re-assigned by the user.

# Date (address 05h...bits description)

| Address | Function | Bit 7   | Bit 6                      | Bit 5         | Bit 4         | Bit 3      | Bit 2     | Bit 1 | Bit 0 |  |

|---------|----------|---------|----------------------------|---------------|---------------|------------|-----------|-------|-------|--|

| 05h     | Date     | 0       | 0                          | 20            | 10            | 8          | 4         | 2     | 1     |  |

| Bit     | Symbol   | Value   | Description                |               |               |            |           |       |       |  |

| 7 to 6  | Х        | 0       | Unused; must be set to "0" |               |               |            |           |       |       |  |

| 5 to 0  | Date     | 0 to 31 | This regis                 | ster holds th | he current of | date coded | in BCD fo | rmat  |       |  |

### Month / Century (address 06h...bits description)

| Address     | Function        | Bit 7   | Bit 6      | Bit 5                                     | Bit 4        | Bit 3      | Bit 2    | Bit 1     | Bit 0 |  |

|-------------|-----------------|---------|------------|-------------------------------------------|--------------|------------|----------|-----------|-------|--|

| 06h         | Month / Century | CB1     | CB0        | 0                                         | 10           | 8          | 4        | 2         | 1     |  |

| Bit         | Symbol          | Va      | lue        |                                           | Descr        | Leap Year  |          |           |       |  |

|             | • • • • • •     | CB1     | CB0        |                                           | 2000.        |            |          |           |       |  |

|             |                 | 0       | 0          | Century 2                                 | 20xx (year 2 | 2000 – 209 | 9)       | 2000 = ye | es    |  |

| 7 to 6      | Century         | 0       | 1          | Century 21xx (year 2100 – 2199) 2100 = no |              |            |          |           | C     |  |

| 7 10 0      | Century         | 1       | 0          | Century 22xx (year 2200 – 2299) 22        |              |            |          |           | C     |  |

| 1 1 Century |                 |         |            |                                           | 23xx (year 2 | 2300 – 239 | 9)       | 2300 = ne | 2     |  |

| 5           | Х               | 0       | Unused;    | must be se                                | t to "0"     |            |          |           |       |  |

| 4 to 0      | Month           | 1 to 12 | This regis | ster holds t                              | he current r | month code | d in BCD | format    |       |  |

| Months      |                 | Bit 7   | Bit 6      | Bit 5                                     | Bit 4        | Bit 3      | Bit 2    | Bit 1     | Bit 0 |  |

| January     |                 | Х       | Х          | 0                                         | 0            | 0          | 0        | 0         | 1     |  |

| February    |                 | Х       | Х          | 0                                         | 0            | 0          | 0        | 1         | 0     |  |

| March       |                 | Х       | Х          | 0                                         | 0            | 0          | 0        | 1         | 1     |  |

| April       |                 | Х       | Х          | 0                                         | 0            | 0          | 1        | 0         | 0     |  |

| May         |                 | Х       | Х          | 0                                         | 0            | 0          | 1        | 0         | 1     |  |

| June        |                 | Х       | Х          | 0                                         | 0            | 0          | 1        | 1         | 0     |  |

| July        |                 | Х       | Х          | 0                                         | 0            | 0          | 1        | 1         | 1     |  |

| August      |                 | Х       | Х          | 0                                         | 0            | 1          | 0        | 0         | 0     |  |

| September   |                 | Х       | Х          | 0                                         | 0            | 1          | 0        | 0         | 1     |  |

| October     |                 | Х       | Х          | 0                                         | 1            | 0          | 0        | 0         | 0     |  |

| November    |                 | Х       | Х          | 0                                         | 1            | 0          | 0        | 0         | 1     |  |

| December    | Х               | Х       | 0          | 1                                         | 0            | 0          | 1        | 0         |       |  |

### Years (address 07h...bits description)

| Address | Function | Bit 7   | Bit 6                                                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|----------|---------|----------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 07h     | Years    | 80      | 40                                                       | 20    | 10    | 8     | 4     | 2     | 1     |  |

| Bit     | Symbol   | Value   | Description                                              |       |       |       |       |       |       |  |

| 7 to 0  | Years    | 0 to 99 | This register holds the current year coded in BCD format |       |       |       |       |       |       |  |

# 3.5. CONTROL SECTION

### Frequency Compensation (address 08h...bits description)

| Address | Function           | Bit 7   | Bit 6                                                                                                 | Bit 5       | Bit 4       | Bit 3  | Bit 2 | Bit 1 | Bit 0 |  |

|---------|--------------------|---------|-------------------------------------------------------------------------------------------------------|-------------|-------------|--------|-------|-------|-------|--|

| 08h     | Freq. Compensation | OUT     | 0                                                                                                     | Mode        | 16          | 8      | 4     | 2     | 1     |  |

| Bit     | Symbol             | Value   | Description                                                                                           |             |             |        |       |       |       |  |

|         |                    | 0       | When OFIE, AFE and Watchdog register are not set to generate an                                       |             |             |        |       |       |       |  |

| 7       | OUT                | 1       | interrupt, the INT pin 6 becomes logic output reflecting the con<br>this bit 7 "OUT"; See section 4.8 |             |             |        |       |       |       |  |

| 6       | Х                  | 0       | Unused;                                                                                               | must be se  | t to "0"    |        |       |       |       |  |

| 5       | Mode               | 0       | Negative                                                                                              | calibration | ; See secti | on 4.2 |       |       |       |  |

| D       | Mode               | 1       | Positive calibration; See section 4.2                                                                 |             |             |        |       |       |       |  |

| 4 to 0  | Calibration value  | 0 to 31 | This register holds the calibration value coded in binary format                                      |             |             |        |       |       |       |  |

### Watchdog (address 09h...bits description)

| Address | Function        | Bit 7           | Bit 6                                                                                   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|-----------------|-----------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| 09h     | Watchdog        | WD2             | WDM4                                                                                    | WDM3  | WDM2  | WDM1  | WDM0  | WD1   | WD0   |  |  |

| Bit     | Symbol          | Value           | Description                                                                             |       |       |       |       |       |       |  |  |

| 7, 1, 0 | WD2 / WD1 / WD0 | 000<br>-<br>100 | Watchdog Timer Clock Source: 16Hz / 4Hz / 1 Hz / ¼ Hz / <sup>1</sup> / <sub>60</sub> Hz |       |       |       |       |       |       |  |  |

| 6 to 2  | WDM4 to WDM0    | 0 to 31         | This register holds the binary coded Watchdog Multiplier value                          |       |       |       |       |       |       |  |  |

### Month Alarm (address 0Ah...bits description)

| Address | Function    | Bit 7   | Bit 6                                                   | Bit 5     | Bit 4       | Bit 3    | Bit 2 | Bit 1 | Bit 0 |  |

|---------|-------------|---------|---------------------------------------------------------|-----------|-------------|----------|-------|-------|-------|--|

| 0Ah     | Month Alarm | AFE     | CLKOE                                                   | 0         | 10          | 8        | 4     | 2     | 1     |  |

| Bit     | Symbol      | Value   | Description                                             |           |             |          |       |       |       |  |

| 7       | AFE         | 0       | Disables Alarm Flag                                     |           |             |          |       |       |       |  |

| 1       | AFE         | 1       | Enables Alarm Flag                                      |           |             |          |       |       |       |  |

| 6       | CLKOE       | 0       | Disables CLKOUT (clock output pin 2)                    |           |             |          |       |       |       |  |

| 0       | CLKOE       | 1       | Enables (                                               | CLKOUT (c | lock output | t pin 2) |       |       |       |  |

| 5       | X           | 0       | Unused; must be set to "0"                              |           |             |          |       |       |       |  |

| 4 to 0  | Month alarm | 1 to 12 | This register holds the month alarm coded in BCD format |           |             |          |       |       |       |  |

### Date Alarm (address 0Bh...bits description)

| Address | Function    | Bit 7    | Bit 6                                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|-------------|----------|--------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 0Bh     | Date Alarm  | ARM4     | ARM5                                                   | 20    | 10    | 8     | 4     | 2     | 1     |  |

|         | -           |          |                                                        |       |       |       |       |       |       |  |

| Bit     | Symbol      | Value    | Description                                            |       |       |       |       |       |       |  |

| 7 to 6  | ARM4 – ARM5 | 00 to 11 | Alarm repeat mode; See section 4.4                     |       |       |       |       |       |       |  |

| 5 to 0  | Date alarm  | 1 to 31  | This register holds the date alarm coded in BCD format |       |       |       |       |       |       |  |

### RV-4162

### Hour Alarm (address 0Ch...bits description)

| Address | Function   | Bit 7   | Bit 6                                                  | Bit 5      | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|------------|---------|--------------------------------------------------------|------------|------------|-------|-------|-------|-------|--|--|

| 0Ch     | Hour Alarm | ARM3    | 0                                                      | 20         | 10         | 8     | 4     | 2     | 1     |  |  |

| Bit     | Symbol     | Value   | Description                                            |            |            |       |       |       |       |  |  |

| 7       | ARM3       | 0 / 1   | Alarm rep                                              | peat mode; | See sectio | n 4.4 |       |       |       |  |  |

| 6       | Х          | 0       | Unused; must be set to "0"                             |            |            |       |       |       |       |  |  |

| 5 to 0  | Hour alarm | 0 to 23 | This register holds the hour alarm coded in BCD format |            |            |       |       |       |       |  |  |

### Minute Alarm (address 0Dh...bits description)

| Address | Function     | Bit 7   | Bit 6                                                     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|---------|--------------|---------|-----------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| 0Dh     | Minute Alarm | ARM2    | 40                                                        | 20    | 10    | 8     | 4     | 2     | 1     |  |

|         |              |         |                                                           |       |       |       |       |       |       |  |

| Bit     | Symbol       | Value   | Description                                               |       |       |       |       |       |       |  |

| 7       | ARM2         | 0 / 1   | Alarm repeat mode; See section 4.4                        |       |       |       |       |       |       |  |

| 6 to 0  | Minute alarm | 0 to 59 | This register holds the Minutes Alarm coded in BCD format |       |       |       |       |       |       |  |

### Second Alarm (address 0Eh...bits description)

| Address | Function     | Bit 7   | Bit 6                                                    | Bit 5     | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|--------------|---------|----------------------------------------------------------|-----------|------------|-------|-------|-------|-------|--|--|

| 0Eh     | Second Alarm | ARM1    | 40                                                       | 20        | 10         | 8     | 4     | 2     | 1     |  |  |

| Bit     | Symbol       | Value   | Description                                              |           |            |       |       |       |       |  |  |

| 7       | ARM1         | 0 / 1   | Alarm rep                                                | eat mode; | See sectio | n 4.4 |       |       |       |  |  |

| 6 to 0  | Second alarm | 0 to 59 | This register holds the second alarm coded in BCD format |           |            |       |       |       |       |  |  |

### Flags (address 0Fh...bits description)

| Address           | Function | Bit 7 | Bit 6                                                                                                   | Bit 5      | Bit 4    | Bit 3                      | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------------------|----------|-------|---------------------------------------------------------------------------------------------------------|------------|----------|----------------------------|-------|-------|-------|--|--|

| 0Fh               | Flags    | WDF   | AF                                                                                                      | 0          | 0        | 0                          | OF    | 0     | 0     |  |  |

| Bit               | Symbol   | Value | Description                                                                                             |            |          |                            |       |       |       |  |  |

| 7                 | WDF      | 0     | No watchdog timer timeout error detected                                                                |            |          |                            |       |       |       |  |  |

| 7                 | WDF      | 1     | Watchdog timer timeout error detected, an interrupt will be generated                                   |            |          |                            |       |       |       |  |  |

|                   |          | 0     | No matching alarm condition detected                                                                    |            |          |                            |       |       |       |  |  |

| 6                 | AF       | 1     |                                                                                                         |            |          | ches Alarm<br>Il be genera |       |       |       |  |  |

| 5 to 3 and 1 to 0 | Х        | 0     | Unused;                                                                                                 | must be se | t to "0" |                            |       |       |       |  |  |

|                   |          | 0     | No oscillator failure timeout error detected                                                            |            |          |                            |       |       |       |  |  |

| 2                 | OF       | 1     | Oscillator failure timeout error detected   If OFIE = 1, an oscillator fail interrupt will be generated |            |          |                            |       |       |       |  |  |

$^{\rm 1)}\,{\rm WDF}$  and AF are read only bits, will be automatically cleared when read.

### RV-4162

# Ultra Small Real Time Clock / Calendar Module

# 3.6. DATA FLOW OF TIME AND DATE FUNCTION

# 3.7. REGISTER RESET VALUE

| Address | Function            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00h     | 10th / 100th Second | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 01h     | Seconds             | 0     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 02h     | Minutes             | 0     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 03h     | Hours               | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 04h     | Day                 | 0     | 0     | 0     | 1     | Х     | Х     | Х     | Х     |

| 05h     | Date                | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 06h     | Month / Century     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 07h     | Years               | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 08h     | Freq. Compensation  | 1     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 09h     | Watchdog            | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0Ah     | Month Alarm         | 0     | 1     | Х     | Х     | Х     | Х     | Х     | Х     |

| 0Bh     | Date Alarm          | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 0Ch     | Hour Alarm          | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 0Dh     | Minute Alarm        | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 0Eh     | Second Alarm        | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| 0Fh     | Flags               | Х     | Х     | Х     | Х     | Х     | 1     | Х     | Х     |

Bit positions labelled as "X" are undefined at power-on and unchanged by subsequent resets.

# 4. DETAILED FUNCTIONAL DESCRIPTION

# 4.1. CLKOUT FREQUENCY SELECTION

The RV-4162 offers the user a programmable square wave clock which is available at CLKOUT pin 2. CLKOUT frequency is programmable by bits FD3 - FD0 (bit 7 - 4 in register Day 04h) according to below table:

| Address | Function   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|---------|------------|-------|-------|-------|-------|--------|-------|-------|-------|

| 04h     | Day        | FD3   | FD2   | FD1   | FD0   | 0      | 4     | 2     | 1     |

| Bit     | Symbol     |       | Val   | ues   |       |        | CLM   | OUT   |       |

| Dit     | Symbol     | FD3   | FD2   | FD1   | FD0   | Frequ  | iency | Unit  |       |

|         |            | 0     | 0     | 0     | 0     | No     | ne    |       | -     |

|         |            | 0     | 0     | 0     | 1     | 32.768 |       | kl    | Ηz    |

|         |            | 0     | 0     | 1     | 0     | 8.1    | 92    | kl    | Ηz    |

|         |            | 0     | 0     | 1     | 1     | 4.0    | 96    | kHz   |       |

|         |            | 0     | 1     | 0     | 0     | 2.048  |       | kHz   |       |

|         |            | 0     | 1     | 0     | 1     | 1.024  |       | kHz   |       |

|         |            | 0     | 1     | 1     | 0     | 512    |       | Hz    |       |

| 7 to 4  | FD3 to FD0 | 0     | 1     | 1     | 1     | 25     | 56    | Hz    |       |

| 7 10 4  |            | 1     | 0     | 0     | 0     | 12     | 28    | Hz    |       |

|         |            | 1     | 0     | 0     | 1     | 6      | 4     | F     | lz    |

|         |            | 1     | 0     | 1     | 0     | 3      | 2     | F     | lz    |

|         |            | 1     | 0     | 1     | 1     | 1      | 6     | F     | lz    |

|         |            | 1     | 1     | 0     | 0     | 8      | 3     | F     | lz    |

|         |            | 1     | 1     | 0     | 1     | 4      | 1     | F     | lz    |

|         |            | 1     | 1     | 1     | 0     | 2      | 2     | F     | łz    |

|         |            | 1     | 1     | 1     | 1     |        |       | F     | lz    |

CLKOUT pin 2 is push-pull output and can be disabled either by setting bits FD3 - FD0 = "0000" or by setting bit CLKOE (bit 6 in register Month Alarm 0Ah) = "0".

### CLKOUT frequency enable / disable (address 0Ah...CLKOE bit description)

| Address | Function    | Bit 7 | Bit 6                                | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------------|-------|--------------------------------------|-------|-------|-------|-------|-------|-------|

| 0Ah     | Month Alarm | AFE   | CLKOE                                | 0     | 10    | 8     | 4     | 2     | 1     |

|         |             |       |                                      |       |       |       |       |       |       |

| Bit     | Symbol      | Value | Description                          |       |       |       |       |       |       |

| 6       | CLKOE       | 0     | Disables CLKOUT (clock output pin 2) |       |       |       |       |       |       |

| 0       | ULNUE       | 1     | Enables CLKOUT (clock output pin 2)  |       |       |       |       |       |       |

Default setting at initial power-up is CLKOUT enabled with the frequency of 32.768 kHz. It is recommended to disable CLKOUT when not used by the application to minimize current consumption of the device.

### RV-4162

# 4.2. FREQUENCY OFFSET COMPENSATION

The frequency offset compensation function gives the end user the ability to calibrate the clock and to improve the time accuracy of the RV-4162.

The RTC is clocked by an oscillator operating a quartz crystal resonator with a nominal frequency of 32.768 kHz. The oscillator frequency on all devices is laser-trimmed and tested not to exceed a time deviation of  $\pm$ 20 ppm at 25°C, which equates to about  $\pm$ 52 seconds per month.

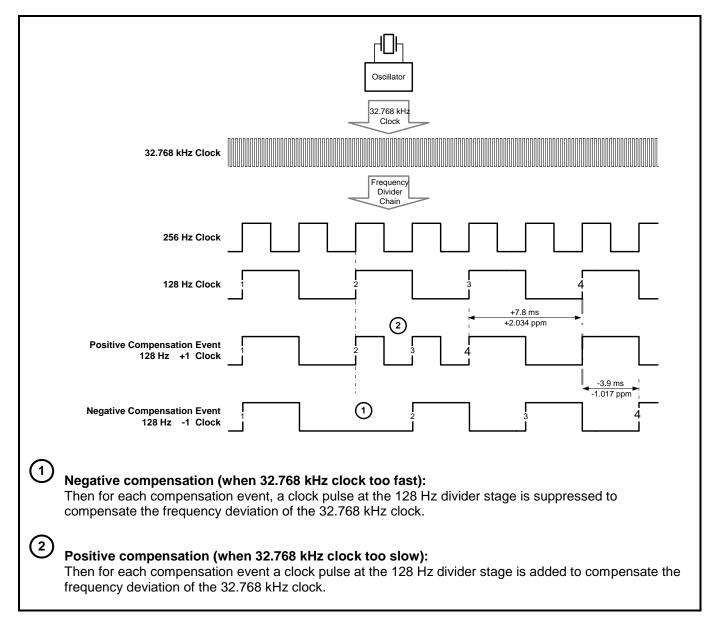

The RV-4162 employs periodic clock counter correction. By properly setting the frequency calibration register in the application, it can improve its time accuracy to typically  $\pm 2$  ppm at 25 °C. The frequency compensation is made by adding or subtracting clock correction counts from the oscillator divider chain at 128 Hz ("divide by 256 stage"), thereby changing the period of a single second.

The number of clock pulses which are subtracted (negative calibration) or added (positive calibration) depends upon the value loaded into the five compensation bits (bit 0 to bit 4) of the Frequency Compensation Register. Adding counts speeds the clock up; subtracting counts slows the clock down.

The frequency offset compensation is controlled by the Frequency Compensation Register 08h. The calibration value occupies the five LSB's (bit 4 - 0). These bits can be set to represent any value between 0 and 31 in binary format. Bit 5 "Mode" is a sign bit; "1" indicates positive calibration and speeds up the time, "0" indicates negative calibration and slows down the time

|          | Address | Fur   | nction   |          |       | Bit 7   | Bit 6                   | Bit 5      | Bit 4                 | Bit 3               | Bit 2                                 | Bit 1        | Bit 0     |  |

|----------|---------|-------|----------|----------|-------|---------|-------------------------|------------|-----------------------|---------------------|---------------------------------------|--------------|-----------|--|

|          | 08h     | Cal   | ibration | Register |       | OUT     | 0                       | Mode       | 16                    | 8                   | 4                                     | 2            | 1         |  |

|          | Bit     | Syr   | nbol     |          |       | Value   | Description             | ı          |                       |                     |                                       |              |           |  |

|          | 5       | Mo    | de       |          |       | 0       | Negative ca<br>too fast | libration; | compensate            | es time devi        | ation when                            | 32.768 kHz   | clock is  |  |

|          | 5       | NIO   | ue       |          |       | 1       | Positive cali<br>slow   | bration; c | compensates           | s time devia        | e deviation when 32.768kHz clock is t |              |           |  |

|          | 4 to 0  | Cal   | ibration | value    |       | 0 to 37 | This register           | holds the  | calibration v         | alue coded i        | n binary forn                         | nat          |           |  |

|          |         |       |          |          |       |         | Compensatio             | n          | Fre                   | quency Co           | ompensatio                            | on Event     |           |  |

|          | Bit 5   | Bit 4 | Bit 3    | Bit 2    | Bit 1 | Bit 0   | Value in<br>Decimal     | Tin        | ne correctio<br>[ppm] | on                  | Compe                                 | nsation eve  | ent       |  |

|          | 0       | 1     | 1        | 1        | 1     | 1       | +31                     |            | -63.054               | 1 <sup>st</sup> - 6 | 2 <sup>nd</sup> minute,               | 1 event eac  | ch minute |  |

| Negative | 0       | 1     | 1        | 1        | 1     | 0       | +30                     |            | -61.02                | 1 <sup>st</sup> -   | 60 <sup>th</sup> minute               | , 1 event ea | ch minute |  |

| gat      |         |       | :        |          |       |         | :                       |            | :                     |                     |                                       |              |           |  |

| Ne       | 0       | 0     | 0        | 0        | 1     | 0       | +2                      |            | -4.068                | 1 <sup>st</sup> -   | 4 <sup>th</sup> minute,               | 1 event ea   | ch minute |  |

|          | 0       | 0     | 0        | 0        | 0     | 1       | +1                      |            | -2.034                | 1 <sup>st</sup> 8   | <sup>a</sup> 2 <sup>nd</sup> minute   | , 1 event ea | ch minute |  |

|          | 0       | 0     | 0        | 0        | 0     | 0       | 0 <sup>1)</sup>         |            | 0                     |                     | No                                    | correction   |           |  |

|          | 1       | 1     | 1        | 1        | 1     | 1       | -1                      |            | +4.068                | 1 <sup>st</sup> 8   | <sup>2<sup>nd</sup> minute</sup>      | , 1 event ea | ch minute |  |

| ive      | 1       | 1     | 1        | 1        | 1     | 0       | -2                      |            | +8.138                | 1 <sup>st</sup> -   | 4 <sup>th</sup> minute                | , 1 event ea | ch minute |  |

| Positive |         |       |          |          |       |         | -                       |            |                       |                     |                                       |              |           |  |

| Ро       | 1       | 0     | 0        | 0        | 0     | 1       | -30                     |            | +122.04               | 1 <sup>st</sup> -   | 60 <sup>th</sup> minute               | , 1 event ea | ch minute |  |

|          | 1       | 0     | 0        | 0        | 0     | 0       | -31                     |            | +126.108              | 1 <sup>st</sup> - ( | 62 <sup>nd</sup> minute               | 1 event ea   | ch minute |  |

Freq. Compensation (address 08h...bits description)

<sup>1)</sup> Default mode at power-up.

### RV-4162

### 4.2.1. FREQUENCY OFFSET COMPENSATION METHOD

The frequency compensation itself occurs within a 64 minute cycle. Each binary coded calibration value will trigger two compensation events; compensation events are applied once per minute until the programmed calibration value has been implemented. If, for example a binary "1" is loaded into the Frequency Compensation Register, only the first 2 minutes in the 64 minute cycle will contain one compensation event each. If a binary '6' is loaded, the first 12 minutes will be affected, and so on.

Each compensation event either shortens one second by 7.8 ms (256 x 32.768 kHz oscillator clock cycles) or lengthened it by 3.9 ms (128 x 32.768 kHz oscillator clock cycles). Therefore, each calibration value triggers two compensation events resulting in a time adjustment of -2.034 ppm (slower by -0.175 seconds per day) or +4.068 ppm (faster by +0.351 seconds per day) for each of the 31 values of the calibration value.

The maximum calibration value (31d) defines the compensation range of -63.054 ppm (slower by -5.449 seconds per day) or +126.108 ppm (faster by +10.899 seconds per day).

Note that frequency compensation events do not affect the frequency at CLKOUT pin 2.

### 4.2.2. DEFINING FREQUENCY COMPENSATION VALUE

The simplest method for ascertaining the frequency deviation a given RV-4162 is to measure the frequency deviation at CLKOUT pin 2. The measured frequency deviation, then, is transformed into an individual compensation value for this device and programmed into the Frequency Compensation Register (08h).

For test purpose, the following configuration will establish a 32.768 kHz clock at CLKOUT pin 2:

- Bit OS = "0" (bit 7 in register Seconds 01h): enables 32.768 kHz oscillator

- Bits FD3 FD0 = "0001" (bits 7 4 in register Day 04h): select 32.768 kHz CLKOUT frequency

- Bit CLKOE = "1" (bit 6 in register Month Alarm 0Ah): enables CLKOUT pin 2

Please note that this is the default setting at power-up.

The frequency deviation on 32.768000 kHz CLKOUT indicates the degree and direction of time deviation for this device. A frequency deviation of +0.032768 Hz equals to +1 ppm.

For example, a reading of 32.768650 kHz indicates a frequency deviation of +20 ppm (faster by +1.73 seconds per day), requiring negative compensation value of "-10d" (xx001010) to be loaded into the Frequency Compensation Register (08h) for frequency compensation.

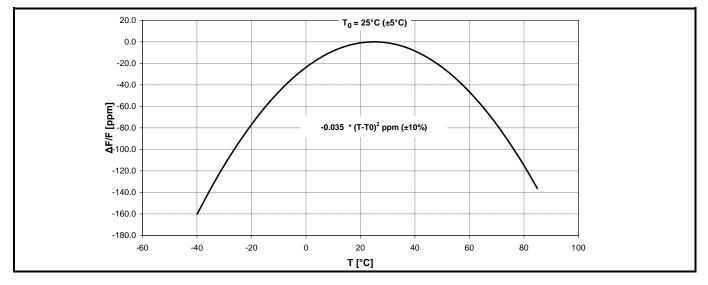

It's important to define the frequency compensation value at an ambient temperature (around 25°C) because of the crystal's frequency vs. temperature characteristics shown on page 29.

### 4.3. WATCHDOG TIMER

The Watchdog Timer can be used to detect an out-of-control microprocessor or deadlock of the Interface communication. The function of the Interface Watchdog Timer is based on internal Timer / Counter which is periodically reset by the internal control logic. If the control logic does not reset the Watchdog Timer within the programmed time-out period, the RV-4162 detects an Interface time-out and sets Watchdog Flag (WDF = 1, bit 7, in register Flags 0Fh) and generates an interrupt on  $\overline{INT}$  pin 6.

The user programs the Watchdog Timer by setting the desired amount of time-out into the Watchdog register at address 09h, a value of 00h will disable the watchdog function until it is again programmed to a new value.

The amount of time-out is then determined by selecting a Watchdog Timer Source Clock WD2 - WD0 and the multiplication with the Watchdog Multiplier value WDM4 - WDM0.

- Bits WDM4 WDM0 store a binary coded Watchdog Multiplier value.

- Bits WD2 WD0 select the Watchdog Timer Clock Source.

For example: writing 00001110 in the Watchdog register =  $3 \times 1$  second or 3 seconds.

### Watchdog (address 09h...bits description)

| Add     | ress | Function | n               |       | Bit 7           | Bit 6                                                                                 | Bit 5                                                                                              | Bit 4                                  | Bit 3         | Bit 2   | Bit 1    | Bit 0 |

|---------|------|----------|-----------------|-------|-----------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------|---------------|---------|----------|-------|

| 0       | 9h   | Watchdo  | g               |       | WD2             | WDM4                                                                                  | WDM3                                                                                               | WDM2                                   | WDM1          | WDM0    | WD1      | WD0   |

| B       | Bit  | Symbol   |                 |       | Value           |                                                                                       |                                                                                                    |                                        | Description   | ı       |          |       |

| 7 t     | o 0  | Watchdo  | g               |       | 00h             | A value of                                                                            | f 00h disable                                                                                      | es Watchdo                             | g Timer fun   | ction   |          |       |

| 7, 1, 0 |      | WD2 / W  | WD2 / WD1 / WD0 |       | 000<br>-<br>100 | Watchdog Timer Clock Source: 16Hz / 4Hz / 1 Hz / $\frac{1}{4}$ Hz / $\frac{1}{60}$ Hz |                                                                                                    |                                        |               |         |          |       |

| 6 t     | o 2  | WDM4 to  | WDM4 to WDM0    |       |                 | 1 This register holds the binary coded Watchdog Multiplier value                      |                                                                                                    |                                        |               |         |          |       |

| WDM4    | WDM3 | WDM2     | WDM1            | WDM0  | Value           |                                                                                       |                                                                                                    | Description                            |               |         |          |       |

| 0       | 0    | 0        | 0               | 0     | 00h             |                                                                                       | g "00000" with any combination of WD2 - WD0, other than "000"<br>in an immediate watchdog time-out |                                        |               |         | 0", will |       |

| 0       | 0    | 0        | 0               | 1     | 01d             |                                                                                       |                                                                                                    | 0                                      |               |         |          |       |

|         |      |          |                 |       |                 | Defines h                                                                             | inary coded                                                                                        | Watchdog                               | Multiplier va | مىالىم  |          |       |

| 1       | 1    | 1        | 1               | 0     | 30d             | Dennes b                                                                              |                                                                                                    | wateridog                              |               |         |          |       |

| 1       | 1    | 1        | 1               | 1     | 31d             |                                                                                       |                                                                                                    |                                        |               |         |          |       |

| WD2     | WD1  | WD0      |                 | Value |                 | Timer                                                                                 | Clock Sou                                                                                          | rce                                    |               | Tim     | e        |       |

| 0       | 0    | 0        |                 | 000   |                 | 16 Hz                                                                                 |                                                                                                    | 6                                      | 2.5ms         |         |          |       |

| 0       | 0    | 1        |                 | 001   |                 | 4 Hz                                                                                  |                                                                                                    | 2                                      | 50 ms         |         |          |       |

| 0       | 1    | 0        |                 | 010   |                 | 1 Hz                                                                                  |                                                                                                    | 1                                      | second        |         |          |       |

| 0       | 1    | 1        |                 | 011   |                 | ¼ Hz                                                                                  |                                                                                                    | 4                                      | seconds       |         |          |       |

| 1       | 0    | 0        |                 | 100   |                 | <sup>1</sup> / <sub>60</sub> Hz                                                       |                                                                                                    | 1 minute                               |               |         |          |       |

| 1       | 0    | 1        |                 | 101   |                 |                                                                                       |                                                                                                    | nation, will not enable Watchdog Timer |               |         |          |       |

| 1       | 1    | 0        |                 | 110   |                 |                                                                                       | nvalid combination, will not enable Watchdog Timer                                                 |                                        |               |         |          |       |

| 1       | 1    | 1        |                 | 111   |                 | Invalid co                                                                            | mbination, v                                                                                       | vill not enab                          | le Watchdo    | g Timer |          |       |

The Watchdog time-out period starts when the  $I^2C$  interface communication is initiated. If the control logic does not reset the Watchdog Timer within the programmed time-out period, the RV-4162 detects an Interface time-out and sets the Watchdog Flag (WDF = 1, bit 7, in register Flags 0Fh) and generates an interrupt on  $\overline{INT}$  pin 6.

The Watchdog Timer can only be reset by having the microprocessor perform a WRITE to the Watchdog Register 09h. The time-out period then starts over.

Should the Watchdog Timer time-out, any value may be written to the watchdog register in order to clear the INT pin 6. A value of 00h will disable the watchdog function until it is again programmed to a new value. A READ of the flags register will reset the Watchdog Flag (bit 7; register 0Fh). The watchdog function is automatically disabled upon power-up, and the Watchdog Register is cleared.

Note: A WRITE to any clock register will restart the Watchdog Timer.

### 4.4. ALARM FUNCTION

Addresses locations 0Ah-0Eh contain the alarm settings. The alarm can be configured to go off at a prescribed time on a specific month, date, hour, minute, or second, or repeat every year, month, day, hour, minute, or second.

Bits ARM5 - ARM1 put the alarm in the repeat mode of operation. The table below shows the possible configurations. Codes not listed in the table default to the once per second mode to quickly alert the user of an incorrect alarm setting.

When the clock information matches the alarm clock settings based on the match criteria defined by ARM5 - ARM1, the AF (alarm flag) is set. If AFE (alarm flag enable) is also set, the alarm condition activates the INT pin 6. To disable the alarm, write "0" to the Date Alarm register and to ARM5 - ARM1.

Note: If the address pointer is allowed to increment to the flag register address, an alarm condition will not cause the interrupt / flag to occur until the address pointer is moved to a different address. It should also be noted that if the last address written is the Second Alarm, the address pointer will increment to the flag address, causing this situation to occur.

The INT is cleared by a READ to the Flags register as shown in figure below. A subsequent READ of the Flags register is necessary to see that the value of the alarm flag has been reset to "0".

### Alarm interrupt reset waveform:

| Register address | OEh  | 0Fh | X | 00h    |

|------------------|------|-----|---|--------|

| ALARM FLAG BIT   | (AF) |     | \ |        |

| INT              |      |     |   | HIGH-Z |

### Alarm Repeat Mode Settings (addresses 0Bh to 0Eh, ARM5 to ARM1...bits description)

| Ad   | dress | Functi | ion     |      | Bit 7       | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|------|-------|--------|---------|------|-------------|-------|-------|---------|--------|-------|-------|-------|

| (    | )Bh   | Date A | larm    |      | ARM4        | ARM5  | 20    | 10      | 8      | 4     | 2     | 1     |

| (    | )Ch   | Hour A | larm    |      | ARM3        | 0     | 20    | 10      | 8      | 4     | 2     | 1     |

| (    | )Dh   | Minute | Alarm   |      | ARM2        | 40    | 20    | 10      | 8      | 4     | 2     | 1     |

| (    | DEh   | Secon  | d Alarm |      | ARM1        | 40    | 20    | 10      | 8      | 4     | 2     | 1     |

| ARM5 | ARM4  | ARM3   | ARM2    | ARM1 |             |       |       | Alarm s | etting |       |       |       |

| 1    | 1     | 1      | 1       | 1    | Once per se | econd |       |         |        |       |       |       |

| 1    | 1     | 1      | 1       | 0    | Once per m  | inute |       |         |        |       |       |       |

| 1    | 1     | 1      | 0       | 0    | Once per h  | our   |       |         |        |       |       |       |

| 1    | 1     | 0      | 0       | 0    | Once per da | ау    |       |         |        |       |       |       |

| 1    | 0     | 0      | 0       | 0    | Once per m  | onth  |       |         |        |       |       |       |

| 0    | 0     | 0      | 0       | 0    | Once per ye | ear   |       |         |        |       |       |       |

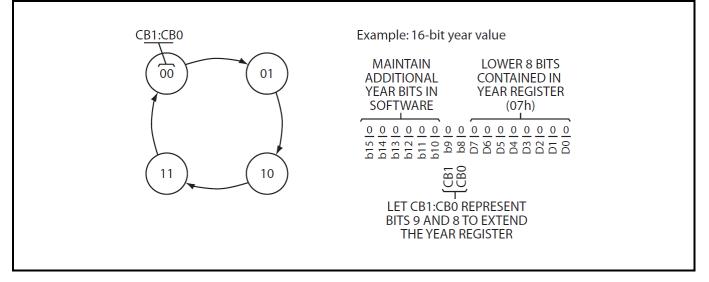

# 4.5. CENTURY BITS

The two century bits, CB1 and CB0, are bits 7 and 6, respectively, in the Month / Century register at address 06h. Together, they comprise a 2-bit counter which increments at the turn of each century. CB1 is the most significant bit.

The user may arbitrarily assign the meaning of CB1:CB0 to represent any century value, but the simplest way of using these bits is to extend the Years register (07h) by mapping them directly to bits 9 and 8 (the reader is reminded that the year register is in BCD format). Higher order year bits can be maintained in the application software.

### Century bits CB1 and CB0:

### 4.6. LEAP YEAR

Leap year occurs every four years, in years which are multiples of 4. For example, 2012 was a leap year. An exception to that is any year which is a multiple of 100. For example, the year 2100 is not a leap year. A further exception is that years which are multiples of 400 are indeed leap years. Hence, while 2100 is not a leap year, 2400 is.

During any year which is a multiple of 4, the RV-4162 RTC will automatically insert leap day, February 29. Therefore, the application software must correct for this during the exception years (2100, 2200, etc.) as noted above.

# 4.7. OSCILLATOR STOP DETECTION

If the oscillator fail (OF) bit is internally set to a "1", this indicates that the oscillator has either stopped, or was stopped for some period of time and can be used to judge the validity of the clock and date data. This bit will be set to "1" any time the oscillator stops.

In the event the OF bit is found to be set to "1" at any time other than the initial power-up, the STOP bit (OS) should be written to a "1", then immediately reset to "0". This will restart the oscillator.

The following conditions can cause the OF bit to be set:

• The first time power is applied (defaults to a "1" on power-up)

Note: if the OF bit cannot be written to "0" four (4) seconds after the initial power-up, the STOP bit (OS) should be written to a "1", then immediately reset to "0".

- The voltage present on  $V_{DD}$  or battery is insufficient to support oscillation

- The OS bit is set to "1"

If the oscillator fail interrupt enable bit (OFIE) is set to a "1", the INT pin 6 will also be activated. The INT output is cleared by resetting the OFIE or OF bit to "0" (NOT by reading the Flag register).

The OF bit will remain set to "1" until written to logic "0". The oscillator must start and have run for at least 4 seconds before attempting to reset the OF bit to "0". If the trigger event occurs during a power-down condition, this bit will be set correctly.

### 4.8. OUTPUT DRIVER PIN

When the OFIE bit, AFE bit, and Watchdog register are not set to generate an interrupt, the INT pin 6 becomes an output driver that reflects the contents of bit 7 (OUT bit) of the Freq. Compensation register. In other words, when bit 7 (OUT bit) is a "0", then the INT pin 6 will be driven low.

Note: The INT pin 6 is an open-drain which requires an external pull-up resistor.

# 5. CHARACTERISTICS OF THE I<sup>2</sup>C BUS

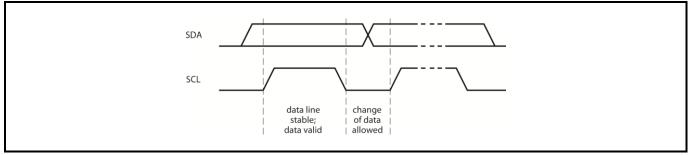

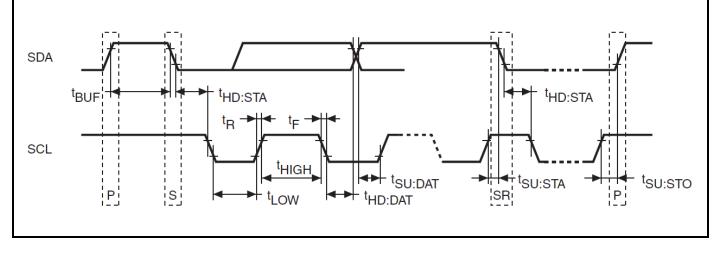

The I<sup>2</sup>C bus is for bidirectional, two-line communication between different ICs or modules. The two lines are a Serial DAta line (SDA) and a Serial CLock line (SCL). Both lines are connected to a positive supply via pull-up resistors. Data transfer is initiated only when the bus is not busy.

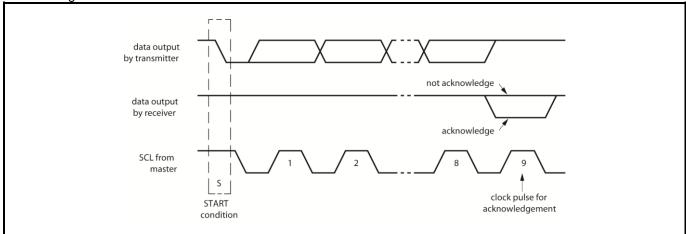

### 5.1. BIT TRANSFER

One data bit is transferred during each clock pulse. The data on the SDA line remains stable during the HIGH period of the clock pulse, as changes in the data line at this time are interpreted as a control signals. Data changes should be executed during the LOW period of the clock pulse (see figure below).

Bit transfer:

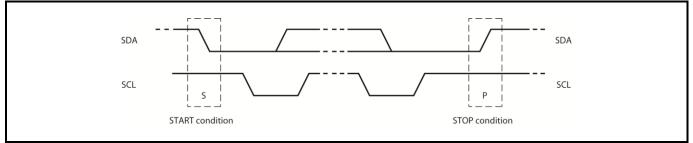

# 5.2. START AND STOP CONDITIONS

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH, is defined as the START condition (S). A LOW-to-HIGH transition of the data line, while the clock is HIGH, is defined as the STOP condition (P) (see figure below).

Definition of START and STOP conditions:

For this device, a repeated START is not allowed. Therefore, a STOP has to be released before the next START.

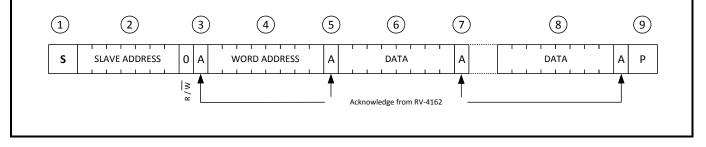

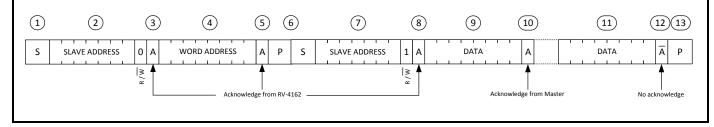

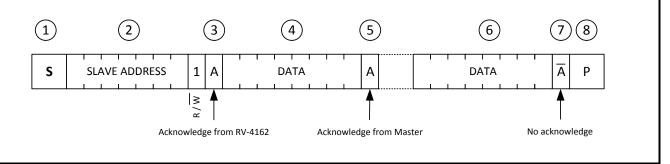

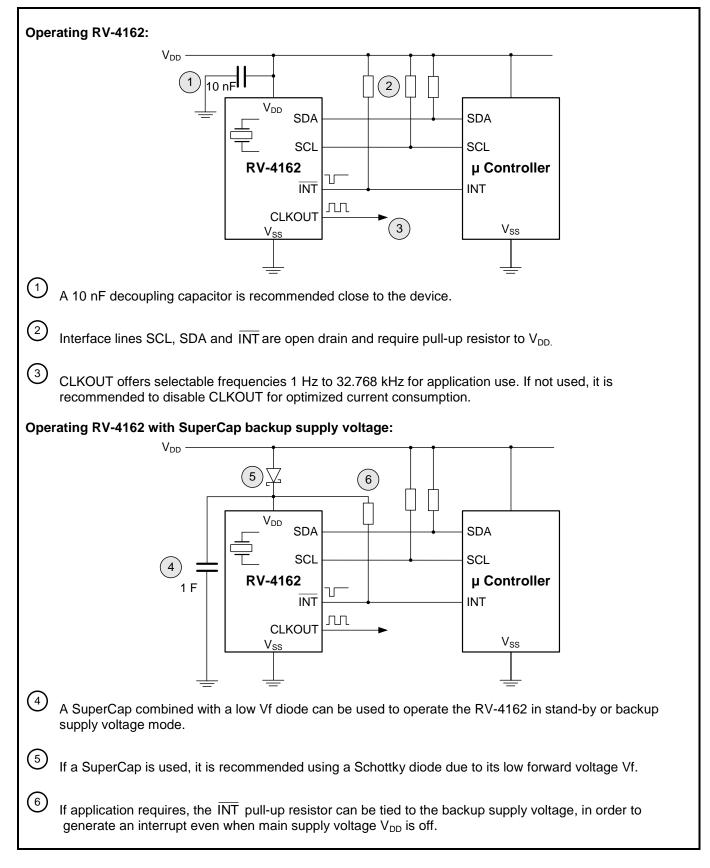

### 5.3. SYSTEM CONFIGURATION